# DIGITALIZADOR DE VIDEO PARA AERONAVES CON SISTEMAS DE VIGILANCIA CON VIDEO ANALÓGICO

JHONNY ALEXANDER BUSTOS VERA CÓDIGO 2005101629 DIEGO IVÁN GARCÍA VARGAS CÓDIGO 2004202331

UNIVERSIDAD SURCOLOMBIANA FACULTAD DE INGENIERÍA INGENIERÍA ELECTRÓNICA NEIVA-HUILA 2011

# DIGITALIZADOR DE VIDEO PARA AERONAVES CON SISTEMAS DE VIGILANCIA CON VIDEO ANALÓGICO

JHONNY ALEXANDER BUSTOS VERA CÓDIGO 2005101629 DIEGO IVÁN GARCÍA VARGAS CÓDIGO 2004202331

DIRECTOR

JAVIER HUMBERTO RUBIO

INGENIERO ELECTRÓNICO

Trabajo de grado presentado como requisito para optar al título de Ingeniero Electrónico

> UNIVERSIDAD SURCOLOMBIANA FACULTAD DE INGENIERÍA INGENIERÍA ELECTRÓNICA NEIVA-HUILA 2011

| Nota de aceptación:             |

|---------------------------------|

|                                 |

|                                 |

|                                 |

|                                 |

|                                 |

|                                 |

|                                 |

|                                 |

|                                 |

|                                 |

|                                 |

|                                 |

|                                 |

|                                 |

|                                 |

| Firma del presidente del jurado |

|                                 |

|                                 |

|                                 |

| Firma del jurado                |

|                                 |

|                                 |

|                                 |

| Firma del jurado                |

# **CONTENIDO**

|                                                                                                                                                                                                                                                 | Pág.                                               |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| RESUMEN                                                                                                                                                                                                                                         | 9                                                  |

| INTRODUCCIÓN                                                                                                                                                                                                                                    | 11                                                 |

| 1. CONCEPTOS GENERALES 1.2 SEÑAL DE VIDEO RS170-A 1.3 DIGITALIZACIÓN Y COMPRESIÓN DEL VIDEO 1.4 DSPIC 1.5 COMPUTADOR EMBEBIDO 1.6 ALMACENAMIENTO                                                                                                | 13<br>14<br>15<br>16<br>16                         |

| 2. HARDWARE 2.1 FUENTES DE SUMINISTRO DE ENERGÍA 2.2 DECODIFICADOR DE VIDEO 2.3 DECODIFICADOR DE AUDIO 2.4 CODIFICADOR DE VIDEO MPEG 2 2.5 DSPIC 2.6 COMPUTADOR EMBEBIDO 2.7 PROGRAMADOR PICKIT 3 2.8 DISEÑO Y FABRICACION DEL CIRCUITO IMPRESO | 17<br>18<br>19<br>22<br>23<br>27<br>27<br>29<br>30 |

| 3. DISEÑO DE FIRMWARE Y SOFTWARE 3.1 MANEJO DE REGISTROS 3.2 SOFTWARE 3.3 CONTROL DE LAS CONFIGURACIONES DE OPERACIÓN                                                                                                                           | 32<br>32<br>35<br>36                               |

| 4. ANÁLISIS DEL PROCESAMIENTO DE LAS SEÑALES<br>4.1 SEÑALES DE SINCRONIZACIÓN DE VIDEO<br>4.2 PROCESAMIENTO SEÑALES EN EL CODIFICADOR                                                                                                           | 39<br>39<br>42                                     |

| 5. CONCLUSIONES                                                                                                                                                                                                                                 | 44                                                 |

| 6. RECOMENDACIONES                                                                                                                                                                                                                              | 46                                                 |

| BIBLIOGRAFÍA                                                                                                                                                                                                                                    | 47                                                 |

| ANEXOS                                                                                                                                                                                                                                          | 48                                                 |

# **LISTA DE FIGURAS**

|                                                            | Pág. |

|------------------------------------------------------------|------|

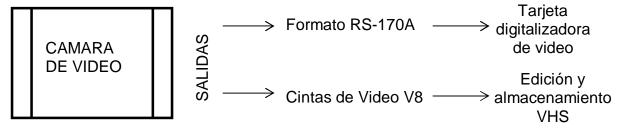

| Figura 1. Diagrama esquemático Sistema video analógico     | 13   |

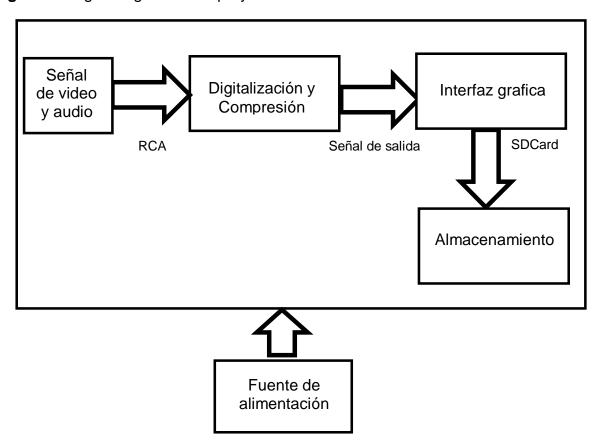

| Figura 2. Diagrama general del proyecto                    | 14   |

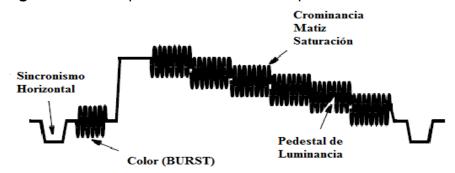

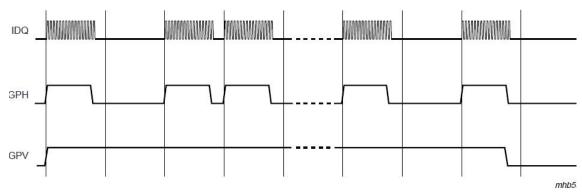

| Figura 3. Señales presentes en video compuesto             | 15   |

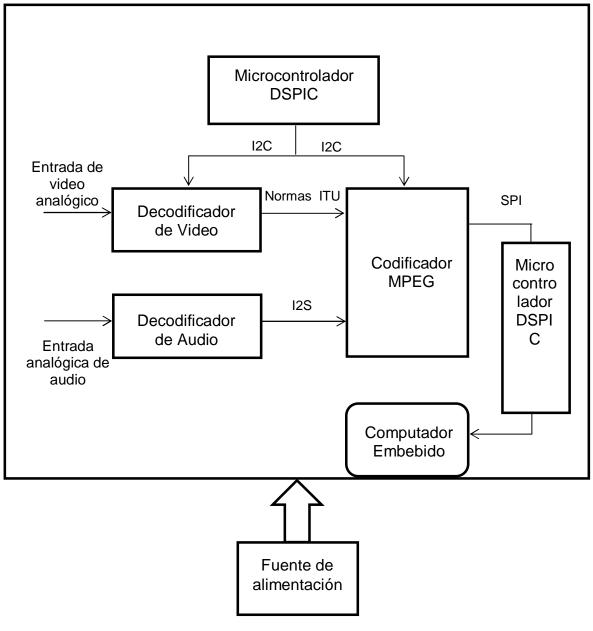

| Figura 4. Diagrama de bloque de Hardware                   | 17   |

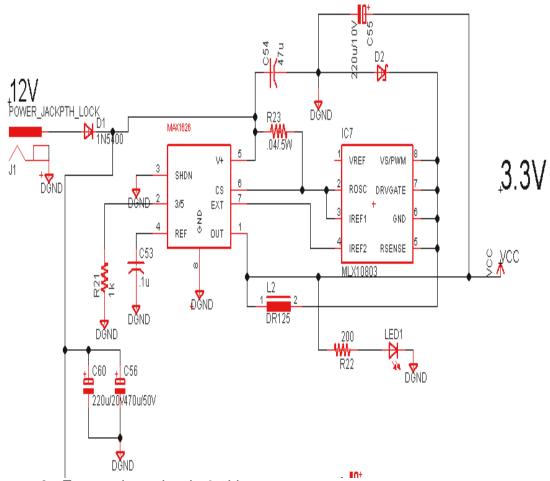

| Figura 5. Fuente de poder de 3.3V                          | 18   |

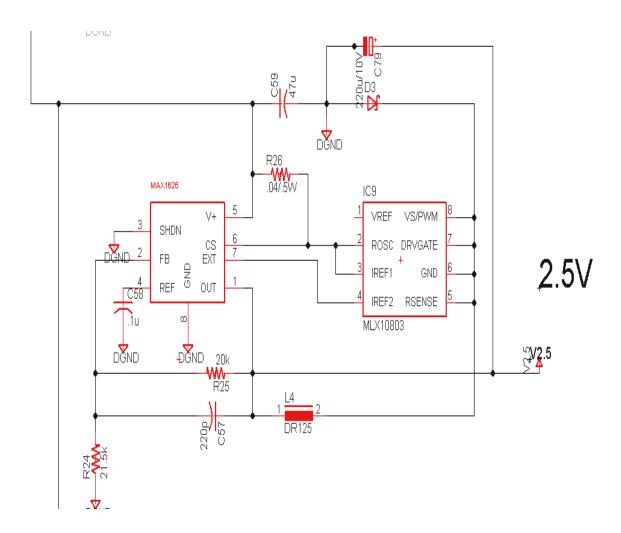

| Figura 6. Fuente de poder de 2.5V                          | 19   |

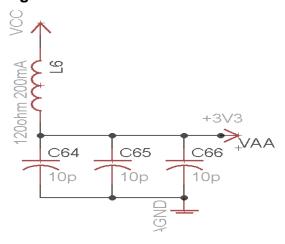

| Figura 7. Filtro                                           | 20   |

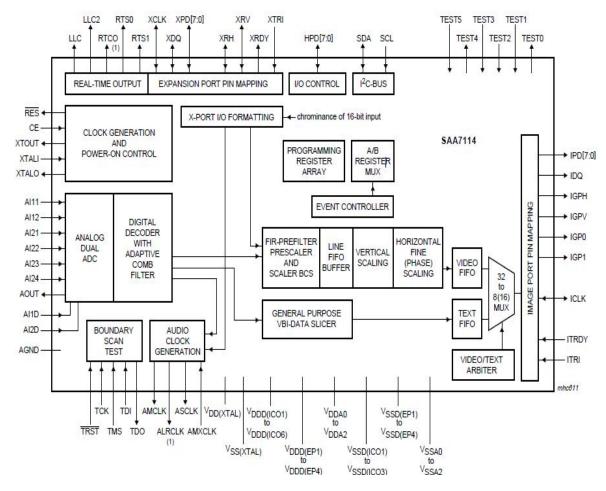

| Figura 8. Diagrama de Bloques del hardware del SAA7114H    | 21   |

| Figura 9. Señales de sincronismo                           | 21   |

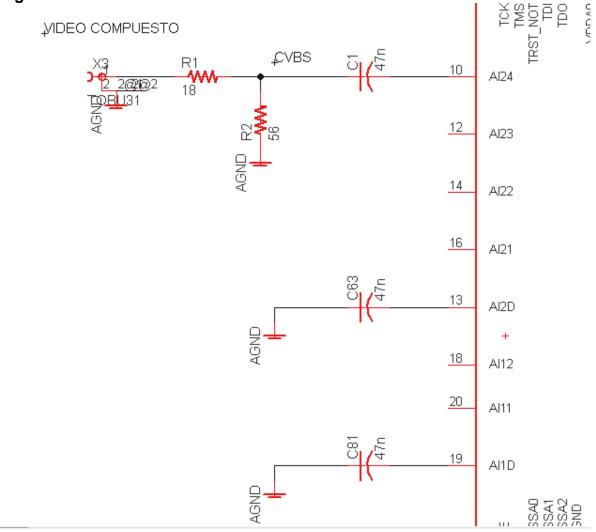

| Figura 10. Canales de entrada                              | 22   |

| Figura 11. Decodificador de audio                          | 23   |

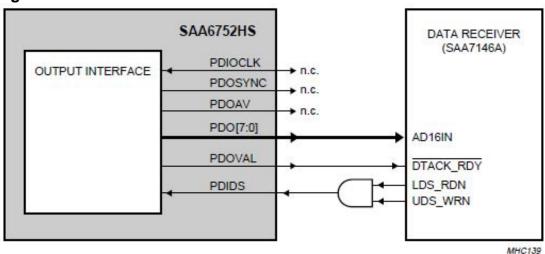

| Figura 12. Conexión en el modo DEBI                        | 24   |

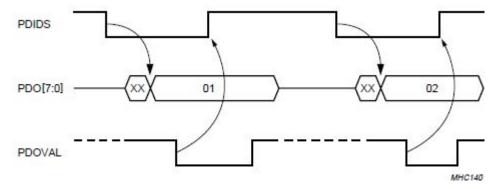

| Figura 13. Transferencia de datos en el modo DEBI          | 25   |

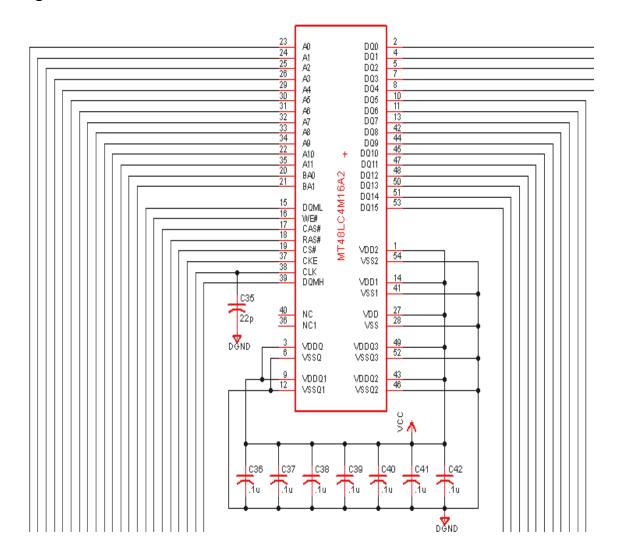

| Figura 14. SDRAM                                           | 25   |

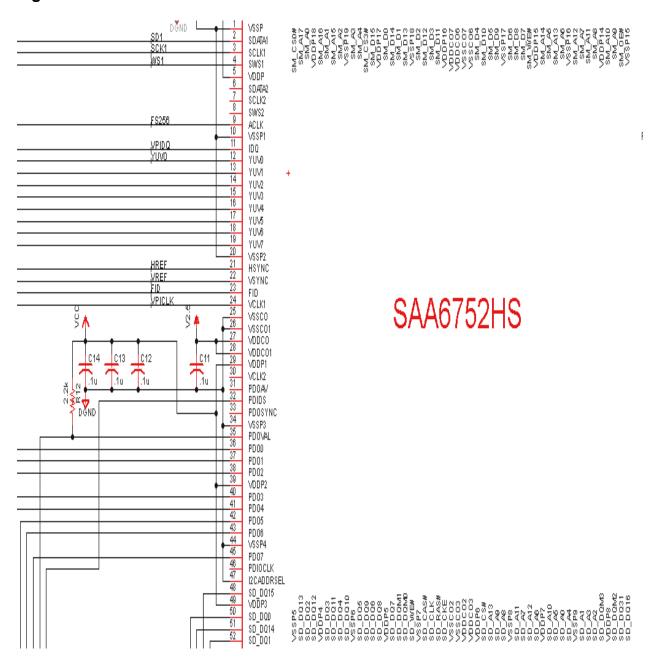

| Figura 15. Codificador de video SAA6752HS                  | 26   |

| Figura 16. Control I2C                                     | 27   |

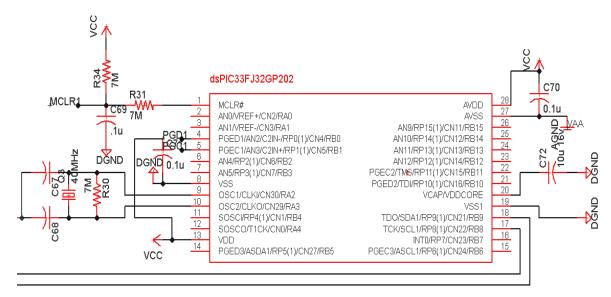

| Figura 17. Entrada y tasa de datos                         | 28   |

| Figura 18. Mini2440                                        | 29   |

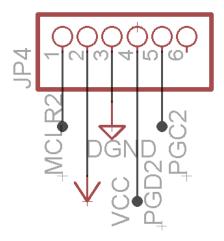

| Figura 19. Pines de programación                           | 30   |

| Figura 20. Circuito impreso (PCB)                          | 31   |

| Figura 21. Comandos de escritura en comunicación I2C       | 32   |

| Figura 22. Modos de operación SAA6752HS                    | 34   |

| Figura 23. Interfaz                                        | 36   |

| Figura 24. Diagrama de flujo de configuración del software | 37   |

| Figura 25. Control de las configuraciones                  | 38   |

| Figura 26. FID                                             | 39   |

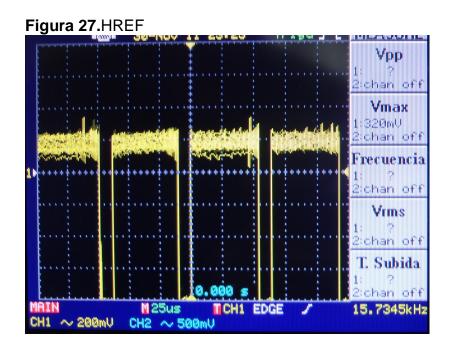

| Figura 27. HREF                                            | 40   |

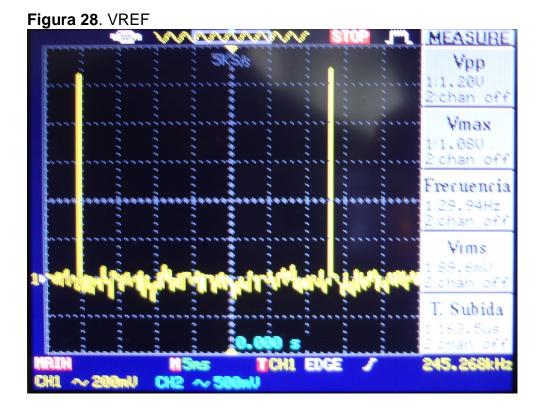

| Figura 28. VREF                                            | 40   |

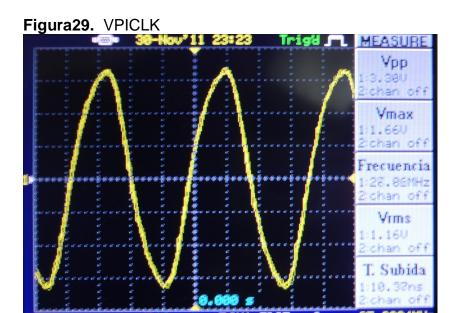

| Figura 29. VPICLK                                          | 41   |

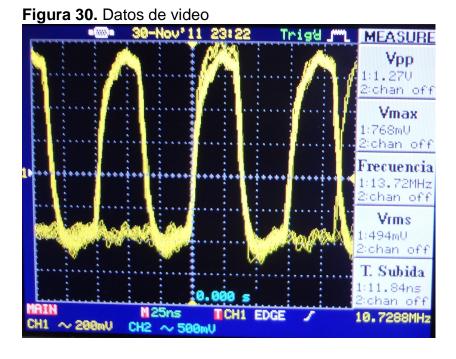

| Figura 30. Datos de video                                  | 41   |

| Figura 31. Datos de salida sin comprimir                   | 42   |

| Figura 32. Datos de salida comprimidos                     | 42   |

# **LISTA DE CUADROS**

|                                                       | Pág. |

|-------------------------------------------------------|------|

| Cuadro 1. Configuración de registro para el SAA7114H  | 33   |

| Cuadro 2. Configuración de registro para el SAA6752HS | 34   |

# **LISTA DE ANEXOS**

|                              | Pág. |

|------------------------------|------|

| ANEXO A. LISTA DE MATERIALES | 48   |

| ANEXO B. CIRCUITO FINAL      | 50   |

#### **GLOSARIO**

CODIFICADOR: Dispositivo que cambia las principales características de un tipo de información a otro, la información puede ser de diferentes orígenes, como video y audio.

COMPUTADOR EMBEBIDO: Dispositivo móvil el cual soporta diferentes sistemas operativos, posee varios de los puertos más comunes, tiene diferentes memorias como la RAM, ROM, NAND Flash y NORFlash.

DEBI: Por sus siglas en ingles(DATA EXPANSION BUS INTERFACE) se usa como una interfaz para implementación con diferentes interfaces como la PCI.

DECODIFICADOR: En algunos procesos es necesario restablecer la información original, como en procesos de transmisión de la televisión digital, por lo tanto esta es su principal función.

DSPIC: Microcontroladores con arquitectura incorporado para el procesamiento digital de señales.

MICROCONTROLADOR: Es un circuito integrado programable con diferentes recursos como los de un computador normal con un procesador, memoria RAM y memoria ROM y diferentes módulos que se pueden usar en diferentes aplicaciones.

MPEG-2: Algoritmo para la compresión video y audio regido por las normas de sus creadores (grupo de expertos en movimiento). Existen algunas versiones de este algoritmo como el MPEG-2, esta versión fue mejorada para diferentes aplicaciones de imágenes.

NTSC: Organización responsable del estándar norteamericano de televisión para la codificación transmisión y recepción de la televisiónanalógica.

RS-170A: Estándar norteamericano para la televisión en blanco y negro, en el cual se definen el sincronismo, numero de líneas, resolución y voltajes de las señales.

#### RESUMEN

El proyecto consiste en diseñar e implementar un digitalizador de video para aeronaves que cuentan con sistemas de video-vigilancia analógico. Implementación que resulta ser un avance tecnológico de gran importancia en las misiones emprendidas por los helicópteros tipo arpía, los cuales en la actualidad, cuentan con un sistema de video-vigilancia obsoleto, que consiste en grabar las misiones de las aeronaves de vigilancia colombiana mediante cintas de video V8.

El sistema cuenta con alimentación de 28 voltios para que pueda ser conectado a la batería del helicóptero tipo arpía, objeto del presente proyecto.

Se diseñó un sistema digitalizador de video totalmente electrónico y portable, utilizando integrados de la marca reconocida Phillips, controlados mediante un microcontrolador, con piezas de peso liviano, solucionando uno de los principales problemas del antiguo sistema. Además presenta un mínimo consumo de potencia, que reduce el volumen y el peso, generando mayor autonomía de grabación de videos, bajos costos de mantenimiento, ahorro de energía y fácil manipulación.

El video capturado desde una cámara de video analógica es digitalizado y comprimido, y posteriormente almacenado en una memoria SD Card.

Para realizar la interacción entre el usuario y el sistema de digitalización de video, se hizo uso un computador embebido, que despliega opciones de fácil entendimiento, entre ellas la del almacenamiento del video en una memoria SD Card.

#### ABSTRACT

The project consists on the design and implementation of a video digitalizer for aircrafts equipped with analogic video-surveillance systems. Implementation that turns out to be a technological advance of great importance on missions taken by Arpía command helicopters, which currentlyhave a video-surveillance system obsolete, that just records the missions of the Colombian security watch aircrafts through V8 video tapes.

The system works with a 28 V power supply, so it can be connected to the Arpía command helicopter battery, which was the objective.

An electronic and portable video digitalizing system was designed; by using Philiphs chips, controlled through a microcontroller, with very light weight pieces and a low power compsumption, reaching with all these changes a decrease in the volume and weight of the machine and maintenance costs, with energy saving and easy operation.

The video captured from an analogic security video camera is digitized and compressed, and then stored in a SD Card memory.

To carry out the interaction between user and the video digitalizer, anembeddedcomputer was used, which displays easy understandable options, including storage memory for video in a SD Card format.

## INTRODUCCIÓN

El AH-60L, también denominado Arpía III, es un helicóptero artillado de origen estadounidense, adquirido por la Fuerza Aérea de Colombia para ejecutar labores de combate. Desde su adquisición, se ha complementado con armamento y utilidades tanto internas como externas, adecuadas para satisfacer las necesidades del entorno colombiano. Entre sus componentes electrónicos, se encuentra un sistema de video vigilancia analógico, con formato RS-170A.

En la actualidad, estas aeronaves utilizan un sistema de video vigilancia analógica, basada en la norma estándar RS-170A, o comúnmente conocida como señales de video compuestas, las cuales se pueden obtener a través de conexiones RCA. Este formato de video conlleva a una serie de inconvenientes, tales como un lento proceso de almacenamiento, manipulación y edición del video analógico,un sistema obsoleto sin compatibilidad con nuevas tecnologías, alto costode mantenimiento de cintas de video y reproductores de videocintas por su poco uso en la actualidad, alto consumo de energía reflejado en pocas horas de grabación,mayor ocupación de espacio en la aeronave por la cintas de video, peso que ocasiona reducción de horas de vuelo de la aeronave de vigilancia, entre otros problemas.

Por los motivos anteriormente expuestos, mediante el presente Trabajo de Grado, se pretende modernizar el sistema de video-vigilancia de aeronaves tipo Helicóptero Arpía utilizados en el país, creando un sistema de video que digitalice, comprimay almacene los datos de video procesados en una memoria SD Card.

Hoy en día, las tarjetas digitalizadoras de video externas con almacenamiento en un medio extraíble, representan un costo demasiado elevado, además de no cumplir con las especificaciones del estándar RS-170A, debido al poco uso de dicho formato en la actualidad.

Practicidad, eficacia y bajo coste son las principales ventajas que aporta este diseño, dividido en cuatro secciones. El primero de ellos es la creación de una fuente de poder, el segundo paso es la digitalización del video analógico, el tercer pasoes la compresión de dicho video y finalmente, el almacenamiento del video en una memoria SDCard, empleando para ello un computador embebido.

La construcción de dicho proyecto, propone un diseño que permite digitalizar una imagen de 480x320 pixeles, comprimir el audio y video y almacenarlo en un medio extraíble, permitiendo hacer uso de una serie de opciones brindadas por el decodificador y codificador para el tratamiento final de la imagen.

Hoy en día, los sistemas de video digitales portables, son parte importante en el mundo audiovisual, utilizados en hogares, en sistemas de video vigilancia, en la industria, vehículos, televisión digital, entre otras múltiples aplicaciones.

El presente libro consta de cuatro capítulos, el primero de ellos sobre las generalidades del proyecto como son la definición de la señal de video de entrada, dispositivos usados para la digitalización y compresión, características de los microcontroladores, y de los computadores embebidos.

El CapítuloDos ilustra sobre el desarrollo del hardware que conduce a obtener el producto final. Aquí se explica cada una de las etapas realizadas en el montaje, divididos en secciones, desde el bloque de la fuente de poder, hasta la adquisición de los datos de video en un medio extraíble.

El Capítulo Tres se centra en describir el firmware y software del microcontrolador DSPIC y el computador embebido mini2440.

En el cuarto y último capítulo se presenta un análisis sobre las señales procesadas, importantes para el correcto funcionamiento del decodificador y codificador.

Además, se anexa una guía que aporta las principales características para la fabricación del circuito impreso, bloque importante para el correcto funcionamiento del circuito implementado.

#### 1. CONCEPTOS Y GENERALIDADES

El helicóptero posee un sistema quecuenta con una cámara de videoanalógico sujeta e inamovible en el habitáculo del helicóptero que cumple con el formato estándar RS-170A<sup>1</sup>, almacenando el video a través de cintas V8. La reproducción y adquisición final de dichos videos, es llevada a cabo en centros de edición, los cuales cuentan con reproductores especiales para este tipo de formatos de cintas. Lo anterior implica la realización de un sistema de video portable, adecuado a las exigencias de un entorno en donde los tiempos de adquisición, edición y almacenamiento del video son críticos.

Hoy en día, las tarjetas digitalizadoras de video externas con almacenamiento en un medio extraíble, representan un costo demasiado elevado, además de no cumplir con las especificaciones del estándar RS-170A, debido al poco uso de dicho formato en la actualidad. La Figura 1,representa el sistema de video empleado en la actualidad.

Figura 1. Diagrama Sistema de video Analógico

Básicamente el dispositivo diseñado e implementado es una tarjeta digitalizadora de video portable, con la capacidad de almacenar video en una memoria SDCard. A continuación se enumeran las características principales del diseño implementado:

- -Entrada de la señal estándar NTSC y posterior conversión de la señal analógica a digital del video y el audio.

- Compresión de las señales presentes conforme al formato MPEG-2.

- Almacenamiento del video en una memoria SDCard.

En el diagrama de bloques de la Figura 2, representa el diagrama general del proyecto.

<sup>&</sup>lt;sup>1</sup>La señales de video monocromáticas solo presentan su componente de luminancia, es decir blanco y negro.

Figura 2. Diagrama general del proyecto

Un digitalizador de video se emplea para capturar cuadros de video de diferentes formatos tales como NTSC, PAL o SECAM. La mayoría de estos digitalizadores comerciales son diseñados para integrarse a una computadora, utilizando como medio de interconexión el protocolo USB o un bus de datos PCI. La portabilidad es parte esencial de este Proyecto de Grado, prescindiendo de cables o conexiones directas a un computador.

## 1.1 SEÑAL DE VIDEORS-170A

Es el formato compatible con la cámara usada en el helicóptero, aunque el decodificador de video empleado en este proyectorequiereuna entrada de video que cumpla con la norma estándar NTSC, una serie de modificaciones en los registros del decodificador de video hace posible que se emplee solo su componente de luminancia<sup>2</sup>, haciéndolo compatible con el formato estándar RS-170A.

\_

<sup>&</sup>lt;sup>2</sup> Las señales de video monocromáticas solo presentan su componente de luminancia, es decir blanco y negro.

El formato estándar RS-170A, es el formato a blanco y negro utilizado en el continente americano, el cual especifica una frecuencia de 15.75 KHz horizontal y 60Hz vertical.

Básicamente, se refiere al video compuesto, los cuales incluyen las señales de video, pulsos sincrónicos horizontales y verticales, pulsos de blanqueo vertical y horizontal y señales especiales, todas combinadas en una sola señal llamada video compuesto.

Esta señal de video contiene toda la información necesaria para ser desplegada en un medio audiovisual, línea por línea y campo por campo. Con ello se obtiene una imagen completa de 525 líneas muestreada 60 veces por segundo. De esas líneas, solo las líneas pares e impares son mostradas en cada cuadro. Para reducir el parpadeo, la imagen se puede dividir en dos campos entrelazados: el primero consta de 262.5 líneas impares (1,3,5...) y el segundo de 262.5 líneas pares (2,4,6...). Con ello, se obtiene una imagen completa de 525 líneas en 1/30 segundos.

La señal de audio se presenta totalmente aparte de la señal de video compuesto. Esta posee un ancho de banda entre los 10Hz y 20kHz

La siguiente Figura 3 representa las señales presentes en un sistema NTSC

Figura3. Señales presentes en video compuesto

Fuente: http://ntsc-tv.com/ntsc-index-03.htm

#### 1.3 DIGITALIZACION Y COMPRESION DEL VIDEO

Este bloque es el encargado de digitalizar la señal analógica. Los datos son comprimidos dentro de un flujo de datos digital (acorde a la normaITU-R-BT.656)<sup>3</sup>, la cual es enviada al codificador de video para ser comprimida deacuerdo a los

<sup>&</sup>lt;sup>3</sup> Constituyen unas series de normas técnicas usadas para implementar en una transferencia de video digital dentro de las normas NTSC y PAL.

estándares de codificaciónMPEG-2. Dicho estándar es complejo y costoso de implementar, pero se reproduce en tiempo real en cualquier equipo de bajo coste.

#### 1.4DSPIC

Este bloque es el encargado de controlar los dispositivos de digitalización y compresión. Además, enviar los datos a través del protocolo SPI al bloque de almacenamiento e interfaz gráfica.

#### 1.5COMPUTADOR EMBEBIDO

Este bloque es el encargado de la interacción entre el sistema digitalizador de video portable y el usuario final, implementado a través de un computador embebido, el cual es un sistema capaz de realizar una o más funciones especiales en tiempo real. Este sistema consta de una CPU, memoria interna o externa, protocolos de comunicación del tipo RS-232, SPI, I2C, USB, IP, WIFI, etc. Módulos de entrada y salida analógicos y digitales, conversores A/D y D/A, filtros, pantalla táctil, módulos de energía y reloj, pines de propósito general (GPIO), puertos USB y SDCard, entre otros.

#### 1.6 ALMACENAMIENTO

Un dispositivo de almacenamiento masivo puede proporcionar acceso a los datos para cualquier propósito.

Implementar la función de almacenamiento masivo es una solución para sistemas que necesiten leer o escribir grandes cantidades de datos. Es por ello, que se utilizan las memorias SD Card.

Las memorias SDCard están disponibles con capacidades de entre 4 MB hasta32 GB. La transferencia de datos es de aproximadamente 15-20 MB/s, en un rango de voltaje entre 2.7 V a 3.6 V.

## 2. HARDWARE

Esta sección describe el diseño y la implementación del hardware. Existen cinco áreas importantes en el diseño: Fuentes de Alimentación, Decodificador de Video y de Audio, Codificador MPEG, interface I2C e interface SPI. Un diagrama de bloques funcional es representado en la Figura 4.

Figura 4. Diagrama de bloques del Hardware

## 2.1 FUENTES DE SUMINISTRO DE ENERGÍA

Para la distribución de alimentación hacia los diferentes dispositivos, se requieren los suministros de voltaje de 2.5V y 3.3V, como se muestra en las Figuras 5y 6. Para ello, se energiza el circuito a 12V+, el cual es convertido a 2.5VDC y 3.3VDC.

Se debe utilizar un regulador de voltaje MAX1626, el cual es un conversor de DC a DC que provee alta eficiencia en la carga, y tiene la capacidad de reducir el suministro de energía para cargas ligeras. Junto con un transistor MOSFET P (MLX10803) y otra circuitería externa adicional. El MAX1626 permite flexibilidad para aplicaciones con requerimientos de potencia de 12W. En las siguientes Figuras se presentan los diagramas esquemáticos detallados de las fuentes implementadas.

Figura 5. Fuente de poder de 3.3V

Figura 6. Fuente de poder de 2.5V

Además, en la Figura 7 se observa un filtro LC implementado para separar las alimentaciones analógicas de las digitales, presentes en el decodificador de video.

#### 2.2 DECODIFICADOR DE VIDEO

Como se mencionó anteriormente, es necesario digitalizar y decodificar los bitsde datos del video, acorde a la normaestándar ITU-R-BT 656. Para esta etapa se utiliza el decodificador de video SAA7114H de Philips. Este decodificador es un procesador de video que cumple con todos los detalles pertinentes al manejo de una señal de video, tales como sincronía, filtros anti-aliasing, manejo del color, control automático de ganancia y afianzamiento del voltaje de la señal analógico de entrada.

Los datos de entrada son convertidos dentro de un paquete de datos (ITU-R-BT. 656), para ser enviados al codificador MPEG.

En la Figura 8 se observa el diagrama de bloques de las principales partes del SAA7114H. El conversor A/D acepta señales de video compuesto (CVBS) yseparado (Y/C)<sup>4</sup>, además es compatible con la resolución D1<sup>5</sup> para el control de las principales funciones a través del bus I2C.

Figura 7. Filtro

El decodificador de video posee seis entradas analógicas modificables mediante selectores internos, pudiendo configurar las entradas de acuerdo a las necesidades del usuario. En este proyecto, se escogió la configuración interna de seis entradas de video compuesto (CVBS).

El decodificador SAA7114 genera cinco señales importantes: datos, sincronismo vertical y horizontal, identificador de campo y señal de reloj de video. En la Figura 9, se observan algunas de estas señales.

Sus pines de alimentacion son conectados respetando el tipo de energizacion, ya sea digital o analógica. Esto es muy importante, puesto que se pueden presentar fallas en el circuito, causando interferencias, cortos circuitos y un mal funcionamiento del dispositivo si son mal conectados.

Figura8. Diagrama de Bloques del hardware del SAA7114H

<sup>5</sup>Resolución de 720X480 pixeles

20

<sup>&</sup>lt;sup>4</sup> Separado Y/C se refiere al formato de video S-video

**Fuente:** NXP,SAA7114 documento en Pdf: http://www.nxp.com/search?q=SAA7114&type=keyword&rows=10

Figura9. Señales de sincronismo

**Fuente:** NXP, SAA7114 documento en Pdf: http://www.nxp.com/search?q=SAA7114&type=keyword&rows=10

En la siguiente Figura se observa la conexión de los canales de entrada. Al utilizarse solamente un canal, los otros canales se desacoplan con un condensador para evitar interferencias con señales parasitas.

Figura10. Canales de entrada

## 2.3 DECODIFICADOR DE AUDIO

El UDA1361TS es un digitalizador de audio que muestrea a 96Khz. Es de bajo consumo de potencia y posee filtrado de señales indeseables. Los datos de audio digitalizados son enviados al codificador MPEG a través del protocolo I2S. (ver Figura 11).

Este dispositivo no necesita de control de sus funciones básicas ya que es un conversor análogo digital básico.

Entrada audio izquierda UDA1361 VINL VDDA 15 VREF VSSA 3 14 VINR MSSEL 4 13 VRN DATAO £ntrada audio derecha 5 12 VRP WS 11 SFOR BCK 10 PWON VSSD 2@21@2 8 9 SYSCLK VDD A GN 131 R17 **--₩₩** 47k R16 **- ₩₩** 47k DĞND DĞND R18 ES256 C47 C48 47u .1u

Figura 11. Decodificador de audio

## 2.4 CODIFICADOR DE VIDEO MPEG-2

El codificador de video es la etapa más importante del diseño. Luego de la digitalización y decodificación, es necesario reducir la cadencia de datos de video para que ocupe menos espacio en memoria, cuyo dispositivo implementado es el SAA6752HSde Philips, el cual posee 208 pines con diferentes funciones.

En estaetapa se incorporó una memoria SD-RAM de soporte para los procesos temporales del codificador de video.

Las entradas de video y audio son comprimidas de acuerdo al estándar MPEG-2 video y MPEG-1 audio y luego multiplexadas dentro de un único paquete de datos. La salida de los datos en formato MPEG, son enviados al microcontrolador usando el protocolo de comunicación DEBI(Data Expansion Bus Interfase).

Para la interconexión con el decodificador de audio, el SAA6752HS cuenta con entradas en formatos I2S o EIAJ, además, posee dos puertos de entrada para los datos de audio, y una velocidad de muestreo a 48Khz para la conversión.

Además, el codificador de video es capaz de generar diferentes tipos de paquetes de flujos de datos de salida como: transporte de tasa de datos (TS), tasa de datos de programa MPEG-2(PS), paquetes de tasa de datos elementales (PES) y tasa de datos elemental(ES). Cada uno de ellos puede ser programado mediante el HOST. Con el paquete de flujos de datos seleccionado, el SAA6752HS cuenta con dos interfaces de salidaDEBI y DIO. En este proyecto se implementó el protocolo DEBI por su facilidad de operación al tener que generar solo una señal de control y detección para datos válidos (PDIDS). En la Figura 12 y 13 se observa la conexión y transferencia en el modo DEBI.

Figura 12. Conexión en el modo DEBI

**Fuente:** NXP, SAA6752HS documento en Pdf:

http://www.nxp.com/search?q=SAA6752HS&type=keyword&rows=10

La información de video es pre-procesado y guardado temporalmente en una memoria SDRAM externa de soportecomo lo muestra la Figura 14.La tasa de datos de salida puede ir desde 1.3Mbit/s hasta 25Mbit/s, y ser variable o constante.

Figura 13. Transferencia de datos en el modo DEBI

Fuente: NXP, SAA6752HS documento en Pdf:

http://www.nxp.com/search?q=SAA6752HS&type=keyword&rows=10

Figura 14. SDRAM

En laFigura se observa algunas de las entradas utilizadas en el codificador con respecto al decodificador de video.

Figura15. Codificador de video SAA6752HS

#### 2.5DSPIC

El microcontroladorDSPIC33FJ32GP202 de microchip es el encargado de manejar las funciones del codificador y decodificador de video. Este se configura como maestro para la comunicación con los dispositivos (decodificador y codificador de video) que son los esclavos, controlando las funciones básicas del codificador y decodificador por medio del protocolo de comunicación serial I2C.

Para realizar la comunicación I2C solo es necesario la conexión de dos líneas, una de datos y la otra de reloj. (Figura 16)

Figura 16. Control I2C

El DSPIC33FJ32GP202 es el dispositivo apropiado para el procesamiento de las señales digitales, su rapidez de procesamiento es ideal para detectar y transmitir bits a alta velocidad. El sistema implementado gestiona los datos comprimidos en formato MPEG-2, para recibirlos y guardarlos temporalmente y posteriormente transmitirlos a una memoria SD Card. El esquemático con sus respectivas conexiones se observa en la Figura 17

#### 2.6 COMPUTADOR EMBEBIDO

El mini2440 es un económico y practico computador embebido basado en una placa de desarrollo ARM.

HILE RES EM PD001 PD002 PD003 PD005 PD007 PD009AL PDIDS R35 C77M dsPIC33FJ326P202

AVSS

AN9/RP15(1)/CN11/RB15

AN10/RP14(1)/CN12/RB14

AN11/RP13(1)/CN13/RB13

AN12/RP12(1)/CN14/RB12 PGEC2/TM6/RP11(1)/CN15/RB11

VCAP/VDDCORE

VSS1 18

17

16

DGND

VDD 3.2k

PGED2/TDI/RP10(1)/CN16/RB10

TDO/SDA1/RP9(1)/CN21/RB9

TCK/SCL1/RP8(1)/CN22/RB8

PGEC3/ASCL1/RP6(1)/CN24/RB6

INTO/RP7/CN23/RB7

ANO/VREF+/CN2/RAO

AN1/VREF-/CN3/RA1

AN4/RP2(1)/CN6/RB2

AN5/RP3(1)/CN7/RB3 VSS

OSC1/CLKI/CN30/RA2

OSC2/CLKO/CN29/RA3

SOSCI/RP4(1)/CN1/RB4

SOSCO/T1CK/CNO/RA4

PGED3/ASDA1/RP5(1)/CN27/RB5

12

13

PGED1/AN2/C2IN-/RP0(1)/CN4/RB0

PGEC1/AN3/C2IN+/RP1(1)/CN5/RB1

Figura 17. Entrada y tasa de datos

En la Figura 18, se observan las principales partes con dimensiones de 100x100(mm). Es un dispositivo muy completo y eficiente para muchas aplicaciones, cuenta con la mayoría de puertos que tiene un computador normal, como interfaz Ethernet RJ-45, 3 puertos seriales, un Host USB, un dispositivo USB, una interface SDCard, una entrada de audio y otra de salida, un micrófono,4 leds para pruebas, 6 botones de usuario, una EEPROM I2C, 20 pines para una interface con una cámara, 34 pines de propósito general entre otros. El procesador es marca SamsungS3C2440A, el cual funciona normalmente a una frecuencia de 400MHz, además, tiene incorporado un sistema de reset, memoria SD-RAM de 32Mbyte para determinadas aplicaciones, conversor análogo a digital, PWM Buzzer, 20 pines JTAG y maneja LCD's con dimensiones que van desde 3.5" hasta 12.1" y resolución de 1024x768 pixeles.

Figura 18. Mini2440

**Fuente:**FriendlyARM,Donwload, user manual, documento en Pdf: http://www.friendlyarm.net/dl.php?file=mini2440\_manual.pdf

La transferencia de los datos digitales desde el microcontrolador DSPIC se hace por medio del protocolo SPI, a una tasa de datos de 1Mbits/seg. Este protocolo SPI se usa a través de los pines de propósito general del mini2440.

#### 2.7 PROGRAMADOR PICKIT 3

El pickit 3 es utilizado para programar y depurar los microcontroladores de la familia Microchip. Los microcontroladores al ser de montaje superficial, su programación debe hacerse en caliente, con el pickit 3 se realiza dicha función,con solo agregarle los dos pines de programación como se observa en la Figura 19.

Figura 19. Pines de programación

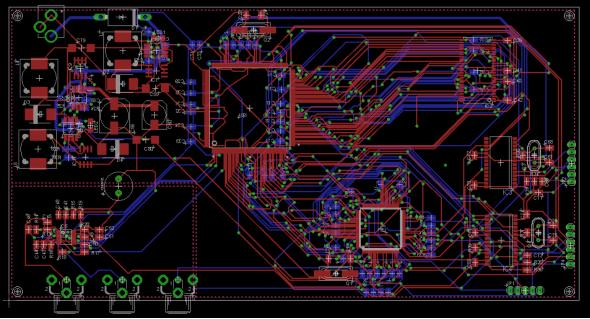

## 2.8 DISEÑO Y FABRICACION DEL CIRCUITO IMPRESO

La ventaja de utilizar montaje superficial se basa en su reducido tamaño, ausencia de hilos y bajo consumo de potencia. Como primera medida, debido al poco uso de estos dispositivos por parte de la comunidad estudiantil, el software Eagle no cuenta con las librerías de tales dispositivos. Es así, que el primer paso en el diseño del circuito impreso, es crear dichas librerías, asegurándose que sus dimensiones sean exactas a las del dispositivo, además de que sus PAD (área plana conductiva donde se realiza la soldadura de los componentes)sean los correctos, en total se han creado 8 librerías de los siguientes dispositivos: SAA7114HS, SAA6752HS, UDA1361, MaX1627, MAX1627, MOSFET N45572, DSPIC33fj32Gp202 y SDRAM.

El siguiente paso es seguir una serie normas, entre las que se encuentra el correcto diseño de las pistas teniendo en cuenta la longitud, grosor y máxima soportada. Para determinar el grosor y la longitud recomendable es necesario revisar la hoja de datos del fabricante de los diferentes dispositivos. Igualmente en la web, se encuentra gran cantidad de software que determinan y calculan las dimensiones de pista a usar según parámetros solicitados. El correcto diseño de estas dimensiones son muy importantes, puesto que si estas quedan mal diseñadas, podrán incrementar el valor de una resistencia no deseada, causar problemas por caídas de tensión, desfase entre líneas de datos y reflejos de estas.

Por ser un circuito de alta frecuencia, las curvas de las pistas no deben superar un ángulo de 45°, ya que podría producirse una auto inducción sobre la misma, deformando su señal. En la Figura 20, se puede observar el diseño final del circuito impreso a doble cara.

Finalmente, se debe generar un archivo GEBER, el cual es el necesario para la fabricación del circuito impreso por medio de técnicas especializadas.

Figura 20. Circuito impreso (PCB)

Como se observa, es importante darle una ubicación a los dispositivos que facilite la interconexión entre ellos, además de separar las etapas de alimentación con las etapas de controly sus alimentaciones analógicas de las digitales.

Es importante mencionar que este circuito se ha diseñado cumpliendo todas las normas internacionales<sup>6</sup> concernientes con el diseño de placas impresas, con sus respectivos planos a tierra.

<sup>&</sup>lt;sup>6</sup>IEC (International Electrotechnical Commission) e IPC (Association Connecting Electronics Industries)

## 3. DISEÑO DEL FIRMWARE Y SOFTWARE

El diseño del firmware se basa en el control de los dispositivos de decodificación, codificación y en el manejo y almacenamiento delos datos, control que es realizado a través de protocolos de comunicación sencillos como el I2C.

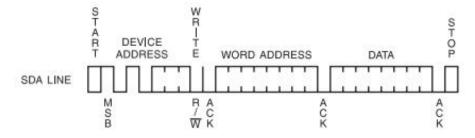

#### 3.1 MANEJO DE REGISTROS

El decodificador y codificador de video, son controlados por medio de una serie de registros, los cuales se encargan de darle unas características y funciones a la señal de video deseada.

El compilador usado fue el MPLAB IDE v8.8, complementado con el MPLAB C Compiler v3.30, suministrado por Microchip.

Para usar el bus de comunicaciones I2C es necesario tener dos o más dispositivos: un dispositivo I2C maestro y uno o más dispositivos esclavos. En este proyecto se usó un microcontrolador Pic18f877A, el cual actúa como maestro, capaz de controlar a los dispositivos esclavos conectados a el, en este caso, el digitalizador y codificador de video (SAA7114H y SAA6752HS respectivamente).

Existen dos tipos de operación en el bus I2C. Estos son comando aleatorio de escritura y comando aleatorio de lectura. En general, un paquete es enviado por el microcontrolador mediante un comando de escritura, como se observa en la Figura 21.

Figura 21. Comandos de escritura en comunicaciones I2C

Fuente: Wikipedia

Tres bytes son enviados a través del microcontrolador, y recibidos por el digitalizador y codificador, de acuerdo a la dirección de dispositivo especificada por el maestro. El primer byte es la dirección de esclavo del dispositivocon su respectivo bit de escritura o lectura, configurando para las funciones de escritura el

bit en 0, esto quiere decir que el maestro escribirá un byte. Si la dirección enviada por el microcontrolador corresponde a la dirección de esclavo de cualquiera de los dispositivos usados, el esclavo devolverá un noveno bit de reconocimiento. Si el bit de reconocimiento es 0, significa que el dispositivo ha sido detectado. La siguiente configuración del bus I2C es la dirección de registro de los dispositivos.

El esclavo vuelve a enviar un bit de reconocimiento, para finalmente enviar los datos a modificar en dicho registro. En el cuadro 1y 2 se observan algunos de los registros configurados que resultan ser imprescindibles a la hora de configurar el digitalizador y codificador de video.

En realidad existen más de 300 registros de configuración, entre los que se encuentra: comienzo y parada de la sincronización, control de sincronización, polaridades de las señales de sincronización, retardos horizontales para emparejar retardos internos de acuerdo a la frecuencia, configuración de la resolución y detección de campo, saturación de la crominancia, contraste de la luminancia, brillantez de la luminancia, fase de crominancia vertical y horizontal, matiz de la crominancia, corrección del offset de la señal análoga, y funciones específicas del SAA7114 como: control de ganancia, señales de los puertos como la de reloj, filtrado de algunas señales indeseables, control de las entradas análogas, definición de los bytes de datos, pines de sincronización, manejo de los diferentes puertos de salida y lectura de los estados de los eventos en el decodificador para detectar errores, entre otros.

Cuadro 1. Configuración de registros para el SAA7114H

| Dirección del dispositivo: 0x42 |                     |                                                                     |

|---------------------------------|---------------------|---------------------------------------------------------------------|

| Dirección<br>del registro       | Ingreso de<br>datos | Función                                                             |

| 0x01                            | 80x0                | Incremento de los retardo en el conversor Análogo<br>a Digital      |

| 0x02                            | 0xc5                | Configuración del tipo de entrada de video a utilizar (Modo 5) CVBS |

| 0x05                            | 0x90                | Control de ganancia en la entrada analógica de video (+6dB)         |

| 0x06                            | 0xeb                | Comienzo de sincronización horizontal                               |

| 0x07                            | 0xe0                | Final de sincronización                                             |

| 0x09                            | 0x40                | Control de luminancia                                               |

| 0x0A                            | 0x80                | Control de brillo de luminancia (Niveles ITU,<br>Oscuro y claro)    |

| 0x0C                            | 0x00                | Control de crominancia (desactivado)                                |

| 0x12                            | 0x00                | Configuración de RTS0 como salida tri estado                        |

Cuadro 2. Configuración de registros para el SAA6752HS

| Dirección del dispositivo: 0x40 |                     |                                                                    |  |

|---------------------------------|---------------------|--------------------------------------------------------------------|--|

| Dirección<br>del registro       | Ingreso de<br>datos | Función                                                            |  |

| 0x10                            | Lectura             | Indica el estado en que se encuentra el dispositivo (ocupado, cod) |  |

| 0x30                            | 0x03                | Configuración del cristal (modo 3)                                 |  |

| 0x40                            | 0x01                | Resolución de salida (524x428)                                     |  |

| 0x06                            | 0xeb                | Comienzo de sincronización horizontal                              |  |

| 0xB1                            | 0x7d0               | Máxima tasa de datos digitales de salida (2Mbits/seg)              |  |

| 0xd0                            | 0x01                | Protocolo de salida (DEBI)                                         |  |

Para activar el codificador MPEG, es necesario enviarlo al modo libre. En la Figura 22se observa los modos de operación del codificador de video MPEG-2 SAA6752HS.

- -Libre: el modo libre puede ser enviado después de reinicializarlo, en este modo se pueden programar la mayoría de registros.

- -Parado: en este modo el procesamiento de video y audio está habilitado, no obstante la multiplexación está deshabilitada.

- -Codificación: en este modo la multiplexaciónde salida es válida e igual que en el modo de parada; solo los parámetros dinámicos pueden ser modificados.

- -Pausado: en este modo se pueden hacer transiciones sin fisuras; reiniciándolo en este modo se puede generar una tasa de datos de salida con sellos de tiempo secuencial.

- -Apagado: en este modo el reloj interno es deshabilitado, enviando el SAA6752HS a un estado no funcional.

Potencia RECONFIGURAR RESET RECONFIGURAR DORMIR **EMPEZAR** PARAR Modo Apagado Parar Codificar Pausar ACTIVO **EMPEZAR** PAUSAR RESET **EMPEZAR**

Figura 22. Modos de operación SAA6752HS

Fuente: NXP, SAA6752HS documento en Pdf:

http://www.nxp.com/search?q=SAA6752&type=keyword&rows=10

El firmware del microcontrolador es el primero en ejecutar el control inicial de las configuraciones del sistema. Al superar esta primera etapa, se activa la generación de nuevos datos que son procesados por el DSPIC. Si se llegaran a presentar errores en la configuración básica de los dispositivos se generaría una interrupción que atienda y verifique el problema. Finalmente los datos de video y audio son enviados a una memoria SDCard.

#### 3.2 SOFTWARE

El sistema operativo utilizado en el mini2440 es el Windows CE 6. Los sistemas operativos soportados por el mini2440, en ninguna de sus versiones implementan drivers del protocolo SPI como una opción de comunicación predeterminada.

Para configurar el protocolo SPI, básicamente, es necesario modificar el kernel<sup>7</sup>del sistema operativoWindows CE. A continuación se enumeran los pasos a seguir desde Visual Studio 2005:

- Instalar Visual Studio 2005 pro, Windows Embedded CE 6.0, service pack 1 de Visual Studio 2005 Pro, service pack of Platform Builder 6.0 y BSP2440 (Board Support Package).

- Abrir en Visual Studio la solución mini2440.

- Configurar la pantalla del mini2440 a W35, mediante el archivo option.h.

- Crear el driver SPI, compilarlo, y posteriormente guardarlo dentro de la solución mini2440, ubicada en la carpeta C:/WINCE600.

- Configurar el registro de drivers de la solución mini2440, agregando los registros de configuración (velocidad, modo y formato) y el canal usado. En este proyecto se usa el canal 1 del protocolo SPI.

- Generar la imagen mediante el comando sysgen. Esta imagen se encuentra en C:/WINCE600/OSDesign/mini2440/Reldir/releasedebug y es llamada NK.bin.

- Finalmente, el archivo generado es usado para la instalación del sistema operativo en el computador embebido mini2440.

El ejecutable guarda automáticamente el video en una memoria SD Card como se observa en la Figura 23.

La interfaz se exportó como una aplicación para que corra en un dispositivo móvil como el min2440.

35

<sup>&</sup>lt;sup>7</sup> Es el corazón del sistema operativo, su función es hacer que el software y hardware trabajen juntos sin complicaciones.

Figura 23. Interfaz

Para la compilación y depuración de este programa, se utilizaron el Visual Studio 2008 y Qtopia 4.3 suministrado por Nokia, el cual es ampliamente utilizado en dispositivos móviles. Qtopia presenta una interfaz muy intuitiva y fácil de manejar, en general, basa su programación en el lenguaje C++ y su interfaz gráfica, y su manejo en general, es muy parecido al Visual Basic de Microsoft Windows.

Inicialmente, el módulo SPI ha sido configurado para que opere a una tasa de transferencia de 1.5 Mbits/seg, pero con la posibilidad de que esta velocidad sea aumentada hasta los 8Mbits/seg.

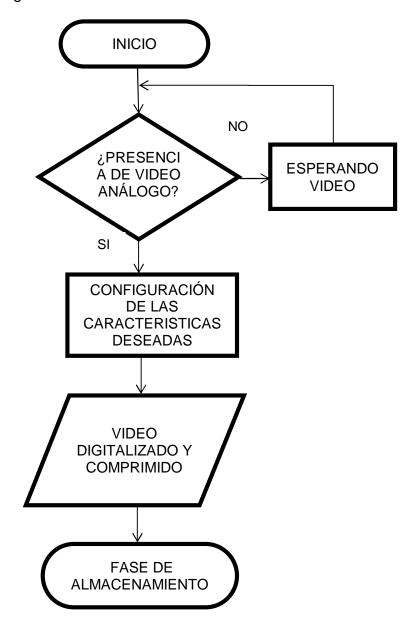

En la Figura 24 se observa el diagrama de flujo del software.

#### 3.3 DIAGRAMA DE FLUJO DEL CONTROL DE LAS CONFIGURACIONES

Como se observa en la Figura 25, se establece la presencia de video en la entrada del conversor A/D y se envía el codificador al modo libre. Cuando se obtienen los requisitos anteriores, se controlan las configuraciones deseadas para satisfacer los estándares de la norma de televisión presente.

En la siguiente etapa se obtiene video digitalizado y comprimido en el formato MPEG-2.

Figura 24. Diagrama de flujo de configuracióndel software INICIO CONFIGURACIÓN **DE LOS PUERTOS** NO **ESPERANDO** ¿NUEVOS DATOS? **DATOS** SI **ENVIANDO** DATOS A LA **MEMORIA** DATOS **ALMACENADOS** ¿TERMINO LA NO TRANSMISIÓN DE DATOS? SI FIN 37

Figura 25. Control de las configuraciones

## 4. ANÁLISIS DEL PROCESAMIENTO DE LAS SEÑALES

Digitalización, procesamiento y manejo de la señal analógica será objeto de los primeros análisis, basados en el decodificador SAA7114.

### 4.1 SEÑALES DE SINCRONIZACIÓN DE VIDEO

La señal FID es usada para determinar si el primer o segundo campo de un cuadro está siendo procesado.

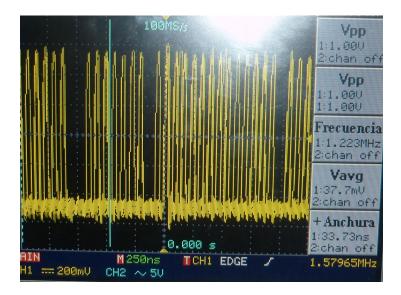

Sujetos a la norma ITU R-BT.656, cuando FID es un cero lógico, significa el primer campo de un cuadro. Esta señal identifica el campo par o impar de video, donde su frecuencia es de 60Hz, en la siguiente Figura se representa la señal FID obtenida.

Figura26.FID

En la Figura 27, se observa la señal de sincronización horizontal (HREF), la cual detecta el fin de una línea de video.

La señal de sincronización VREF es la encargada de marcar el comienzo de cada campo, como se observa en la Figura 28.

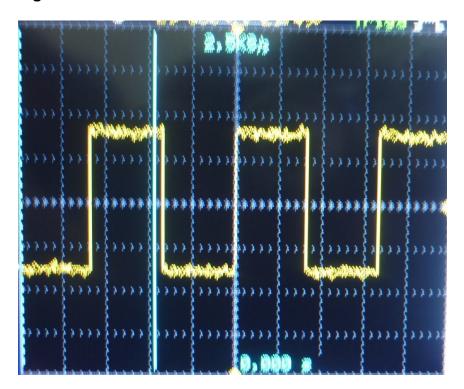

En la siguiente Figura se observa la señal de video de salida *VPICLK*, la cual es de 27 Mhz

Y por último, en este primer bloque de procesamiento se observa en la Figura 30 las señales de datos de video los cuales son 8 bits. Todas las señales son enviadas al codificador de video.

## **4.2 PROCESAMIENTO SEÑALES EN EL CODIFICADOR**

El segundo y último bloque de procesamiento es el codificador de video a MPEG-2 (SAA6752).

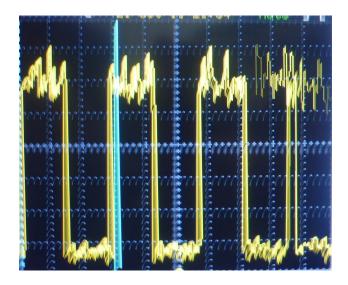

En la Figura 31 se observa las señales que varían en forma y frecuencia ya que son datos de video sin comprimir y comprimidos, que se guardan temporalmente en la memoria SDRAM.

Figura 31. Datos de salida comprimidos

Los datos de salida son ilustrados en la Figura32.

Figura 32. Datos de salida comprimidos

Como se observó en las anteriores imágenes la señal de video es descompuesta en sus principales partes, y enviada al codificador de video formando paquetes de datos en la salida para que sean almacenados dentro de una memoria SDCard.

La tasa de compresión es de 30:1, por ejemplo para dicho proyecto en la digitalización se generan 45 Mbits/seg, y después de la compresión se obtiene una tasa de 1Mbits/segapróximadamente.

Para una memoria SD Card de 2GB, se obtiene aproximadamente 3 horas de grabación, para algunas aplicaciones este tiempo de grabación puede disminuir por aumentar la tasa de bits en la salida de la compresión.

#### 5. CONCLUSIONES

En el presente trabajo de grado se diseñó e implemento un digitalizador de video portable, que cumple con la norma estándar RS170, empleando en la entrada al sistema una señal de video analógica compuesta, generada mediante conexiones RCA.

El decodificador y codificador de video soportan complejos algoritmos de procesamiento, análisis y configuraciones de la señal procesada, brindando múltiples opciones en el momento de tratar las imágenes de acuerdo a las necesidades requeridas por el usuario. La ventaja de estos dispositivos es el permitir diferentes resoluciones de salida, reducción del ruido, diferentes formas de empaquetamiento de datos para aplicar directamente a reproductores de DVD o como en dicho proyecto simplemente almacenamiento de los datos de video.

En los procesos de almacenamiento y transmisión de video muchas veces se necesita reducir la información de video digital que se va a guardar o a transmitir. Una eficaz herramienta es utilizar dispositivos para la compresión de video, que en la actualidad existen comercialmente a un bajo costo, como el codificador de video MPEG-2, el cual es una buena alternativa para reducir la tasa de datos de video.

Finalmente, se logró almacenar el video digitalizado y comprimirlo en una memoria SDCARD, atendiendo todos los requisitos para la velocidad de transferencia de datos de video digitalizados y comprimidos, este objetivo se logró por medio de un computador embebido. La interfaz SPI se escogió como puente de comunicación entre el Hardware y el Software, debido a su tasa de transferencia de alrededor 4 Mbits/seg, velocidad necesaria para procesar y almacenar los datos de video transmitidos por el codificador de video a una tasa de 1.5 Mbits/seg.

La experiencia de programar con Qtopia fue satisfactoria, este software gratuito orientado a objetos es muy similar al Visual Studio, además de poseer mayor cantidad de documentación.

Aunque Qtopia puede funcionar en un entorno Windows, es recomendable implementarlo en la plataforma Ubuntu, puesto que a la hora de compilar y modificar el kernel del sistema operativo es mucho más sencillo que en Windows. Basta con unos pocos comandos en el Hyperterminal para llevar a cabo estas operaciones.

Eagle fue el software escogido para el diseño de la tarjeta (PCB), debido a su facilidad de manejo y amplia documentación. Aunque para los dispositivos empleados en dicho proyecto las librerías no existían, Eagle cuenta con la función de crearlas, y gracias a la gran cantidad de empaquetaduras presentes en el

software, se hace sencilla su creación. En total, fueron creadas ocho nuevas librerías.

Para una correcta fabricación y diseño del hardware, se deben cumplir una serie de recomendaciones. El diseño debe partir de la implementación de un circuito a doble cara, correcto diseño de las pistas teniendo en cuenta la longitud, grosor y máxima corriente que deban conducir, ubicación de los componentes de tal forma que la longitud de las pistas sea lo mas pequeña posible, además de la separación de los bloques de potencia y control, uso de estaciones semiautomáticas y tecnologías de verificación y pruebas de tarjetas electrónicas.

Debido al reducido tamaño de los componentes y a la posibilidad de colocar componentes por ambas caras, se pueden lograr altas integraciones de circuito.

Considerando cada una de las especificaciones planteadas inicialmente y a su vez satisfaciendo el nivel intelectual de los autores, se cumplió con las expectativas de dicho proyecto. Se puede reflexionar en llevar a cabo futuros estudios dentro del país, en lo que respecta a las técnicas de digitalización, comprensión y almacenamiento de video digital, valorando que los avances en el país en estas áreas son menores.

#### 6. RECOMENDACIONES

Diseñar las pistas teniendo en cuenta la longitud y el grosor máximo permitido. Para determinar el grosor y la longitud recomendable es necesario revisar la hoja de datos del fabricante de los diferentes dispositivos. Igualmente en elinternet, se encuentran gran cantidad de software que determinan y calculan las dimensiones de pista a usar según parámetros solicitados. El correcto diseño de estas dimensiones es muy importante, puesto que si estas quedan mal diseñadas, podrán incrementar el valor de una resistencia no deseada, causar problemas por caídas de tensión, desfase entre líneas de datos y reflejos de estas.

Para obtener un correcto funcionamiento del decodificador de video es importante programar una alta ganancia en la entrada del video analógico,a través sus registros de configuración. Si esto no se lleva a cabo, el decodificador no digitalizara ni transmitirá los datos hacia el codificador de video MPEG.

Se debe tener cuidado en el manejo de potencia en una conversión DCa DC ya que si se excede la capacidad de estos conversores, pueden presentarse voltajes incorrectos o daños en los mismos en las etapas siguientes.

Exponer los dispositivos de digitalización y compresión a altas temperaturas puede causar daños irreversibles, situación que puede evitarse ya que cada dispositivo trae en su hoja de datos el rango de temperatura permitido para la soldadura.

Por la gran cantidad de pines que poseen el decodificador y codificador de video se debe tener precaución con las diferentes conexiones entre estos. Igualmente se deben habilitar correctamente los registros para el buen funcionamiento del cristal externo, interfaces de salida y entrada, transferencia de datos de salida, tipos de escaneo entre otros.

Al ser los pines de estos dispositivos, elementos muy frágiles, es necesario tomar todas las precauciones del caso para su manipulación ya que pueden presentarse partiduras lo que conlleva a que no funcionen correctamente. También se debe tener especial cuidado con las cargas electrostáticas, aislaquedos cuerpos mediante una manilla electrostática.

Para futuras mejoras en el proyecto se puede llevar a cabo la modernización del formato de compresión a MPEG-4, también se puede actualizar el computador embebido a una versión mas eficiente como el mini6410, por otra parte también se puede crear diferentes opciones para guardar los datos de video, como memorias USB y MMC. Otro tema importante a desarrollar seria un método para detectar errores o fallas en el sistema.

#### **BIBLIOGRAFIA**

BREIJO GARCIA Eduardo. Compilador C CCS y simulador PROTEUS para Microcontroladores PIC. AlfaomegaGrupo Editor, Mexico, junio de 2008.

Dogan Ibrahim. SD CARD PROJECTS USING THE PIC MICROCONTROLLER. Newnes.

Datasheet Microchip DSPIC33f.

http://ww1.microchip.com/downloads/en/DeviceDoc/70290F.pdf

Datasheet SAA7114H PHILIPS.

http://www.datasheetcatalog.org/datasheet/philips/SAA7114H\_1.pdf

Datasheet SAA6752HS PHILIPS.

http://www.datasheetcatalog.org/datasheet/philips/SAA6752HS\_V103.pdf

Datasheet UDA1361 PHILIPS.

http://www.datasheetcatalog.org/datasheet/philips/UDA1361.pdf

Foro de microcontroladorestodopic www.todopic.com.ar

Constantino Perez Vega. Compresión de video

Norma ITU 601http://webs.uvigo.es/servicios/biblioteca/uit/rec/BT/R-REC-BT.601-6-200701-I!!PDF-S.pdf

Compresión de video MPEG-ITU. Análisis de los métodos de codificación de video mediante técnicas ADPCM, MPEG y las normas del ITU

Manuales mini2440www.friendlyarm.net

Página NTSC http://ntsc-tv.com/index.html

## **ANEXO A. Lista de materiales**

| Item | Cantidad | Numero de parte            | Descripción                         | Precio<br>Unidad | Precio<br>Total |

|------|----------|----------------------------|-------------------------------------|------------------|-----------------|

| 1    | 3        | PIC18F66K22-<br>I/PTRSL-ND | MCU PIC 64K FLASH<br>MEM XLP 64TQFP | 4.72000          | \$14.16         |

| 2    | 3        | RCV420JP-ND                | IC OPAMP GP 150KHZ<br>SGL 16DIP     | 8.88000          | \$26.64         |

| 3    | 2        | PS7341-1A-ND               | SSR OCMOS FET<br>150MA NO 6-DIP     | 2.23000          | \$4.46          |

| 4    | 2        | LM555CMFS-ND               | IC OSC MONO TIMING<br>8-SOP         | 0.45000          | \$0.90          |

| 5    | 2        | 296-6615-1-ND              | IC DUAL DIFF<br>COMPARATOR 8-SOIC   | 0.70000          | \$1.40          |

| 6    | 10       | 311-604CRCT-ND             | RES 604 OHM 1/8W 1%<br>0805 SMD     | 0.02100          | \$0.21          |

| 7    | 10       | 311-1.27KCRCT-ND           | RES 1.27K OHM 1/8W<br>1% 0805 SMD   | 0.02100          | \$0.21          |

| 8    | 2        | PIC18F86K22-<br>I/PTRSL-ND | MCU PIC 64K FLASH<br>XLP 80TQFP     | 5.18000          | \$10.36         |

| 9    | 2        | 296-22072-1-ND             | IC PREC VOLT-CURR<br>CONV/TX 10MSOP | 2.63000          | \$5.26          |

| 10   | 2        | AD8138AARZ-ND              | IC DIFF ADC DVR LOW<br>DISTOR 8SOIC | 6.41000          | \$12.82         |

| 11   | 3        | WM7848-ND                  | CONN HEADER 5POS<br>5.08MM R/A TIN  | 1.77000          | \$5.31          |

| 12   | 3        | WM7821-ND                  | CONN TERM BLOCK<br>5POS 5.08MM      | 3.48000          | \$10.44         |

| 13   | 2        | WM7847-ND                  | CONN HEADER 4POS<br>5.08MM R/A TIN  | 1.40000          | \$2.80          |

| 14   | 2        | WM7953-ND                  | CONN TERM BLOCK<br>4POS 5.08MM R/A  | 3.12000          | \$6.24          |

| 15   | 3        | WM7845-ND                  | CONN HEADER 2POS<br>5.08MM R/A TIN  | 0.92000          | \$2.76          |

| 16   | 3        | WM7819-ND                  | CONN TERM BLOCK<br>2POS 5.08MM      | 1.83000          | \$5.49          |

| 17   | 50       | RG20P1.0KBCT-ND            | RES 1.0K OHM 1/8W .1% 0805 SMD      | 0.24780          | \$12.39         |

| 18   | 50       | RG20P2.0KBCT-ND            | RES 2.0K OHM 1/8W .1%               | 0.24780          | \$12.39         |

| Item | Cantidad | Numero de parte        | Descripción                         | Precio<br>Unidad | Precio<br>Total |

|------|----------|------------------------|-------------------------------------|------------------|-----------------|

|      |          |                        | 0805 SMD                            |                  |                 |

| 19   | 3        | 296-1014-5-ND          | IC OPAMP GP 700KHZ<br>DUAL 8SOIC    | 0.44000          | \$1.32          |

| 20   | 1        | AE10697-ND             | CORD SVT 18AWG<br>3COND SHIELD 1.5M | 6.15000          | \$6.15          |

| 21   | 2        | 296-28008-1-ND         | IC BOOST INV DUAL<br>ADJ 2A 24QFN   | 6.76000          | \$13.52         |

| 22   | 4        | PIC18F1220-I/P-ND      | IC MCU FLASH 2KX16<br>A/D 18-DIP    | 3.72000          | \$14.88         |

| 23   | 4        | PIC18F1320-I/P-ND      | IC MCU FLASH 4KX16<br>A/D 18-DIP    | 4.10000          | \$16.40         |

| 24   | 2        | T1102-P5P-ND           | ADPT MULTI-BLADE<br>5VDC 1.2A P5P   | 10.26000         | \$20.52         |

| 25   | 4        | 732-1175-1-ND          | INDUCTOR POWER<br>4.7UH 2.9A SMD    | 2.70000          | \$10.80         |

| 26   | 20       | PCE3900CT-ND           | CAP ALUM 22UF 25V<br>20% SMD        | 0.43000          | \$8.60          |

| 27   | 1        | P160DACT-ND            | RES 160 OHM 1/8W .1% 0805 SMD       | 0.49000          | \$0.49          |

| 28   | 1        | P180DACT-ND            | RES 180 OHM 1/8W .1%<br>0805 SMD    | 0.49000          | \$0.49          |

| 29   | 1        | P620KDACT-ND           | RES 620K OHM 1/8W<br>.1% 0805 SMD   | 0.49000          | \$0.49          |

| 30   | 1        | PNM0805-5.0KBCT-<br>ND | RES 5.0K OHM .2W 0.1% 0805 SMD      | 2.77000          | \$2.77          |

| 31   | 1        | Mini2440               | COMPUTADOR<br>EMBEBIDO              | 170              | \$170           |

<sup>\*</sup>moneda US dolar

# ANEXO B. Circuito Final